## **Supercharging Programming through Compiler Technology**

by

## William S. Moses

M.Eng., Massachusetts Institute of Technology (2017) S.B., Massachusetts Institute of Technology (2017)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

**Doctor of Philosophy**

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2023

©2023 William S. Moses. All rights reserved.

The author hereby grants to MIT a nonexclusive, worldwide, irrevocable, royalty-free license to exercise any and all rights under copyright, including to reproduce, preserve, distribute and publicly display copies of the thesis, or release the thesis under an open-access license.

Authored by: William S. Moses

Department of Electrical Engineering and Computer Science

May 19, 2023

Certified by: Charles E. Leiserson

Professor of Computer Science and Engineering

Thesis Supervisor

Accepted by: Leslie A. Kolodziejski

Professor of Electrical Engineering and Computer Science

Chair, Department Committee on Graduate Students

## **Supercharging Programming through Compiler Technology**

by

#### William S. Moses

Submitted to the Department of Electrical Engineering and Computer Science on May 19, 2023, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

The decline of Moore's law and an increasing reliance on computation has led to an explosion of specialized software packages and hardware architectures. While this diversity enables unprecedented flexibility, it also requires domain-experts to learn how to customize programs to efficiently leverage the latest platform-specific API's and data structures, instead of working on their intended problem. For example, a researcher hoping to use machine learning on climate code must write a corresponding derivative simulation, understand and implement linear algebra routines, and performance engineer their simulation to run on multiple cores and nodes. Rather than forcing each user to bear this burden, I propose building high-level abstractions within general-purpose compilers that enable fast, portable, and composable programs to be automatically generated.

This thesis will demonstrate this approach through several real-world and composable compilers that I built for a variety of domains including parallelism, automatic differentiation, scheduling, portability, program search, and tensor arithmetic. These domains are critical to both scientific computing and machine learning. Individually, integration of domain knowledge into each of these compilers enable (often asymptotic) performance and usability benefits. Operating on a common compiler representation, however, enables these benefits to compound and provide greater performance than any domain-specific optimization in isolation.

This research in this thesis contains joint work with Charles E. Leiserson, Tao B. Schardl, Nicolas Vasilache, Oleksandr Zinenko, Theodoros Theodoridis, Priya Goyal, Zachary DeVito, Zachary, Sven Verdoolaege, Andrew Adams, Albert Cohen, Qijing (Jenny) Huang, Ameer Haj-Ali, John Xiang, Ion Stoica, Krste Asanovic, John Wawrzynek, Valentin Churavy, Lorenzo Chelini, Ruizhe Zhao, Ludger Paehler, Jan Hückelheim, Sri Hari Krishna Narayanan, Michel Schanen, Johannes Doerfert, Paul Hovland, Ivan R. Ivanov, Jens Domke, and Toshio Endo.

Thesis Supervisor: Charles E. Leiserson

Title: Professor of Electrical Engineering and Computer Science

## Acknowledgments

First and foremost I want to thank my family. I particularly want to thank my sister Sophia Moses, father John Moses, mother Marina Moses, and my pappou Panayoti Stefanidis. Your unwavering love and support have been instrumental to my time at MIT in undergraduate and graduate school.

I'd like to my advisor, Charles E. Leiserson, who has provided constant research and life advice since even before I came to MIT as an undergraduate. I'd like to thank the other members of my committee, Alan Edelman, Albert Cohen, and Saman Amarasinghe for providing advice not just on this thesis, but research and academia at large. I'd like to thank Srini Devadas for showing me how to be a good mentor – a role model I am to emulate as I enter academia. I'd like to thank Jason Ku for tireless work to make teaching fun.

Without a doubt, there are no colleagues of mine who have provided more support, advice (and fun conference excursions) than Valentin Churavy, Alex Zinenko, and Johannes Doerfert. I'd also like to thank my numerous research colleagues, without whom the work in this thesis would not be possible, including: Jed Brown, Hal Finkel, Marco Foco, Leila Gharaffi, Laurent Hascoet, Patrick Heimbach, Paul Hovland, Jan Hueckelheim, Mike Innes, Tim Kaler, Charles Leiserson, Yingbo Ma, Ludger Paehler, Chris Rackauckas, TB Schardl, Lizhou Sha, Yo Shavit, Vassil Vassilev, Sarah Williamson, Pat McCormick, George Stelle, Stephen Olivier, Joanna Balme, Eric Brown-Dymkosky, Victor Guerrero, Stephen Jones, Andre Kessler, Adam Lichtl, Kevin Lung, Ken Museth, Nathan Robertson, Youseef Marzouk, Jesse Michel, Kevin Kwok, Douglas Kogut, Jiahao Li, Bojan Serafimov, Carl Guo, Sanath Govindarajan, Walden Yan, Sage Simhon, Chuyang Chen, Shakil Ahmed, Abhishek Vu, Chris Hill, AJ Root, Teo Collins, Nicolas Vasilache, Zach Devito, Andrew Adams, Lorenzo Chelini, Ruiche Zhao, Sven VErdoolaege, Tim Gymnich, Pratush Das, Manuel Drewalrd, Theodoros Theodoridis, Priya Goyal, Ivan R. Ivanov, Jens Domke, Toshio Endo, John Wawrzynek, Krste Asanovic, Ion Stoica, Jenny Huang, Ameer Haj-Ali, Daniel Dunbar, Neil Thompson, Bill Kuszmaul, Charith Mendis, the Supertech research group, JuliaLab research group, COMMIT resaerch group, the FutureTech research group, and more.

There are so many other friends and colleagues that I would like to thank, that I would quickly use up the remaining ink on the printer. I'd like to thank my lifelong friends I've made from primary school, Joey Cimento, Jeff Saulnier, Mike Timpane, and Joseph Orttung, who remind me to always have fun alongside work. I'd like to thank numerous friends from TJ including Andrew Coffee, Daniel Stiffler, Nalini Singh, Alex Atanasov, Matt Levonian, Will Qian Abi Gopal, Will Bradbury, James Bradbury, and Ryan Jian. I'd like to thank Mark Hannum, Charles Clancy, and John Dell for getting me into research. I'd like to thank my Maseeh pals: Arezu Esmaili, Andreea Martin, Alex Cabrales, Austin Clark, Brook Eyob, Elizabeth Bianchini, Henry Love, Juan Angulo, Mellisa Gianello, Rob Bugliarellia, Rodrigo Ruiz, Allison Tam, Ananya Nandy, Anna Bueno, Claudia Wu, Daphne Lin, Darius Bopp, Elena Albertia, Emily Sheng, Grace Yin, Jason Priest, Joseph Murphy, Kristen Fromback, Niyati Desai, Nola Mulugeta, Rogers Epstein, Ron Dentinger, Travis Hank, and Kevin Sabo. I'd like to thank Andrea Carney for making my time at Sidpac a constant joy. I'd like to thank many other folks including: Bob Knighton, Sofi Peterson, Emma Batson, Tasha Schoenstein, Burhan Azeem, Anne Hunter, Rachel (Cummings) Shavit, Tesla Wells, Crystal Wang, Erica Yuen, Predrag Gruveski Victoria Xia, Shayna Ahtek Botong Ma, Anish Athalye, Kelsey Becker, Lizhou Sha, Alex Chernyakovsky, Angel Alvarez, Alan Sadun, Jamie Voros, Logan Engstrom, Kevin Kwok, Cat Zeng, Zachary Pitcher, Tomas Villalon, Piper Lim, and Chris Peterson.

The research contained within was financially supported in part by numerous organizations. This includes a DOE Computational Sciences Graduate Fellowship DE-SC0019323; NSF Cyberinfrastructure for Sustained Scientific Innovation (CSSI) award numbers: 2104068, 2103942, and 2103804; the Defense Advanced Research Projects Agency (DARPA) under Agreement No. HR0011-20-9-0016; NSF Grant OAC-1835443; Los Alamos National Laboratories grant 531711. Research was sponsored in part by the United States Air Force Research Laboratory and was accomplished under Cooperative Agreement Number FA8750-19-2-1000. The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the United States Air Force or the U.S. Government. The U.S. Government is

authorized to reproduce and distribute reprints for Government purposes notwithstanding any copyright notation herein.

# **Contents**

| 1 | Intr | oductio  | n                                                | 29 |

|---|------|----------|--------------------------------------------------|----|

| 2 | Tapi | ir: A co | ompiler representation for fork-join parallelism | 32 |

|   | 2.1  | Introd   | uction                                           | 32 |

|   |      | 2.1.1    | Previous approaches                              | 34 |

|   |      | 2.1.2    | The Tapir approach                               | 36 |

|   |      | 2.1.3    | Ease of implementation                           | 37 |

|   |      | 2.1.4    | Expressiveness of Tapir                          | 38 |

|   |      | 2.1.5    | Serial semantics                                 | 39 |

|   |      | 2.1.6    | Optimizations                                    | 39 |

|   |      | 2.1.7    | Evaluation of Tapir/LLVM                         | 39 |

|   |      | 2.1.8    | Contributions                                    | 41 |

|   |      | 2.1.9    | Outline                                          | 41 |

|   | 2.2  | Tapir    |                                                  | 41 |

|   |      | 2.2.1    | Tapir instructions                               | 42 |

|   |      | 2.2.2    | Static single-assignment form                    | 44 |

|   |      | 2.2.3    | Asymmetry in Tapir                               | 45 |

|   |      | 2.2.4    | Parallel loops in Tapir                          | 46 |

|   | 2.3  | Analy    | sis passes                                       | 46 |

|   |      | 2.3.1    | Constraints on transformations                   | 47 |

|   |      | 2.3.2    | Alias analysis                                   | 47 |

|   |      | 2.3.3    | Dominator analysis                               |    |

|   |      | 2.3.4    | Data-flow analysis                               |    |

|   | 2.4  | Optimization passes |                                           |    |

|---|------|---------------------|-------------------------------------------|----|

|   |      | 2.4.1               | Common-subexpression elimination          | 50 |

|   |      | 2.4.2               | Loop-invariant code motion                | 51 |

|   |      | 2.4.3               | Tail-recursion elimination                | 51 |

|   |      | 2.4.4               | Parallel-loop scheduling and lowering     | 53 |

|   |      | 2.4.5               | Other optimization passes                 | 53 |

|   | 2.5  | Auxilia             | ary software                              | 54 |

|   | 2.6  | Evalua              | tion                                      | 55 |

|   |      | 2.6.1               | Benchmarking                              | 57 |

|   |      | 2.6.2               | Overall performance                       | 58 |

|   | 2.7  | Relate              | d work                                    | 59 |

|   | 2.8  | Conclu              | asion                                     | 60 |

| 3 | Tens | sor Con             | nprehensions                              | 63 |

|   | 3.1  | Introdu             | action                                    | 63 |

|   | 3.2  | Tensor              | Comprehensions                            | 65 |

|   |      | 3.2.1               | Data Layout                               | 68 |

|   |      | 3.2.2               | Automatic Differentiation                 | 69 |

|   | 3.3  | Tensor              | Comprehensions Workflow                   | 70 |

|   |      | 3.3.1               | Range Inference                           | 71 |

|   |      | 3.3.2               | Lowering to the Polyhedral Representation | 72 |

|   |      | 3.3.3               | Tunable Polyhedral Scheduling             | 74 |

|   |      | 3.3.4               | Imperfectly Nested Loop Tiling            | 76 |

|   |      | 3.3.5               | Mapping to Blocks and Threads             | 77 |

|   |      | 3.3.6               | Memory Promotion                          | 79 |

|   |      | 3.3.7               | Matching Library Calls                    | 80 |

|   |      | 3.3.8               | Autotuning and Caching                    | 81 |

|   | 3.4  | Integra             | ation with ML Frameworks                  | 83 |

|   | 3.5  | Perform             | mance Results                             | 84 |

|   | 3.6  | Relate              | d Work                                    | 03 |

|   | 3.7  | Concl   | usion                                             | 96  |

|---|------|---------|---------------------------------------------------|-----|

| 4 | Auto | oPhase: | : Machine-Learning Assisted Optimization Ordering | 98  |

|   | 4.1  | Introd  | uction                                            | 98  |

|   | 4.2  | Backg   | ground                                            | 102 |

|   |      | 4.2.1   | Compiler Phase-ordering                           | 102 |

|   |      | 4.2.2   | Reinforcement Learning Algorithms                 | 103 |

|   |      | 4.2.3   | Evolutionary Algorithms                           | 104 |

|   | 4.3  | AutoP   | Phase Framework for Automatic Phase Ordering      | 105 |

|   |      | 4.3.1   | HLS Compiler                                      | 105 |

|   |      | 4.3.2   | Clock-cycle Profiler                              | 106 |

|   |      | 4.3.3   | IR Feature Extractor                              | 107 |

|   |      | 4.3.4   | Random Program Generator                          | 107 |

|   |      | 4.3.5   | Overall Flow of AutoPhase                         | 107 |

|   | 4.4  | Correl  | lation of Passes and Program Features             | 109 |

|   |      | 4.4.1   | Importance of Program Features                    | 109 |

|   |      | 4.4.2   | Importance of Previously Applied Passes           | 111 |

|   | 4.5  | Proble  | em Formulation                                    | 112 |

|   |      | 4.5.1   | The RL Environment Definition                     | 112 |

|   |      | 4.5.2   | Applying Multiple Passes per Action               | 113 |

|   |      | 4.5.3   | Normalization Techniques                          | 113 |

|   | 4.6  | Evalua  | ation                                             | 113 |

|   |      | 4.6.1   | Performance                                       | 114 |

|   |      | 4.6.2   | Generalization                                    | 115 |

|   | 4.7  | Concl   | usions                                            | 118 |

| 5 | Enz  | yme: C  | Compiler-based Automatic Differentiation          | 120 |

|   | 5.1  | Introd  | luction                                           | 120 |

|   | 5.2  | Design  | n                                                 | 123 |

|   | 5.3  | Usage   |                                                   | 129 |

|   | 5.4  | Evalua  | ation                                             | 132 |

|   | 5.5  | Concli | usion                                                        | 135 |

|---|------|--------|--------------------------------------------------------------|-----|

| 6 | Poly | geist: | Improving Polyhedral Scheduling Via High-Level Structure And | l   |

|   | Low  | -Level | Optimization                                                 | 136 |

|   | 6.1  | Introd | uction                                                       | 136 |

|   | 6.2  | The M  | ILIR Framework                                               | 138 |

|   |      | 6.2.1  | Overview                                                     | 138 |

|   |      | 6.2.2  | Affine and MemRef Dialects                                   | 139 |

|   |      | 6.2.3  | Other Relevant Core Dialects                                 | 141 |

|   | 6.3  | An (A  | ffine) MLIR Compilation Pipeline                             | 142 |

|   |      | 6.3.1  | Frontend                                                     | 142 |

|   |      | 6.3.2  | Raising to Affine                                            | 145 |

|   |      | 6.3.3  | Connecting MLIR to Polyhedral Tools                          | 146 |

|   |      | 6.3.4  | Controlling Statement Granularity                            | 151 |

|   |      | 6.3.5  | Post-Transformations and Backend                             | 153 |

|   | 6.4  | Evalua | ation                                                        | 155 |

|   |      | 6.4.1  | Experimental Setup                                           | 155 |

|   |      | 6.4.2  | Baseline Performance                                         | 156 |

|   |      | 6.4.3  | Compilation Flows                                            | 157 |

|   | 6.5  | Perfor | mance Analysis                                               | 158 |

|   |      | 6.5.1  | Benchmarking                                                 | 158 |

|   |      | 6.5.2  | Baseline Comparison                                          | 159 |

|   |      | 6.5.3  | Performance Differences in Sequential Code                   | 159 |

|   |      | 6.5.4  | Performance Differences In Parallel Code                     | 160 |

|   |      | 6.5.5  | Case Study: Statement Splitting                              | 161 |

|   |      | 6.5.6  | Case Study: Reduction Parallelization in durbin              | 162 |

|   | 6.6  | Relate | d Work                                                       | 163 |

|   | 6.7  | Discus | ssion                                                        | 165 |

|   |      | 6.7.1  | Limitations                                                  | 165 |

|   |      | 6.7.2  | Opportunities and Future Work                                | 166 |

|   |      | 6.7.3   | Alternatives                                                  | . 167 |

|---|------|---------|---------------------------------------------------------------|-------|

|   | 6.8  | Conclu  | asion                                                         | . 167 |

| 7 | Fast | Autom   | atic Differentiation of GPU Kernels via Compiler Optimization | 168   |

|   | 7.1  | Introdu | uction                                                        | . 168 |

|   | 7.2  | Relate  | d Work                                                        | . 171 |

|   | 7.3  | Autom   | natic Differentiation                                         | . 172 |

|   | 7.4  | Revers  | se-Mode AD for GPU Kernels                                    | . 174 |

|   |      | 7.4.1   | GPU Memory-Aware Gradient Synthesis                           | . 175 |

|   |      | 7.4.2   | Adjoints of Barriers                                          | . 176 |

|   |      | 7.4.3   | GPU Intrinsics and Shared-Memory Allocations                  | . 177 |

|   |      | 7.4.4   | Usage                                                         | . 178 |

|   | 7.5  | Optim   | izations                                                      | . 178 |

|   | 7.6  | Evalua  | ation                                                         | . 185 |

|   |      | 7.6.1   | Setup                                                         | . 186 |

|   |      | 7.6.2   | Benchmark Descriptions                                        | . 188 |

|   |      | 7.6.3   | Results                                                       | . 190 |

|   | 7.7  | Conclu  | asion                                                         | . 196 |

| 8 | Scal | able Au | tomatic Differentiation of Multiple Parallel Paradigms        | 198   |

|   | 8.1  | Introdu | uction                                                        | . 198 |

|   | 8.2  | Relate  | d Work                                                        | . 200 |

|   | 8.3  | AD Ba   | ackground                                                     | . 201 |

|   | 8.4  | Differe | entiation model                                               | . 202 |

|   |      | 8.4.1   | Differentiating parallel tasks                                | . 203 |

|   |      | 8.4.2   | Differentiating message passing                               | . 204 |

|   |      | 8.4.3   | Caching of intermediate results                               | . 204 |

|   | 8.5  | Compi   | iler-Integrated Differentiation                               | . 205 |

|   |      | 8.5.1   | Identifying Parallel Constructs                               | . 206 |

|   |      | 8.5.2   | Differentiating Parallel Constructs                           | . 207 |

|   |      | 8.5.3   | Data caching                                                  | . 207 |

|   |             | 8.5.4   | General Applicability                                       | . 208 |

|---|-------------|---------|-------------------------------------------------------------|-------|

|   |             | 8.5.5   | Optimization and Differentiation                            | . 209 |

|   | 8.6         | Other 1 | Parallel Constructs                                         | . 210 |

|   |             | 8.6.1   | Memory                                                      | . 210 |

|   |             | 8.6.2   | Concurrent Caching                                          | . 213 |

|   |             | 8.6.3   | High-Level Language Constructs                              | . 214 |

|   |             | 8.6.4   | Non-determinism                                             | . 215 |

|   | 8.7         | Evalua  | tion                                                        | . 216 |

|   |             | 8.7.1   | Benchmark Implementation Details                            | . 217 |

|   |             | 8.7.2   | Gradient verification                                       | . 219 |

|   | 8.8         | Result  | s                                                           | . 221 |

|   | 8.9         | Conclu  | usion                                                       | . 223 |

| 9 | Uial        | , Dorfo | rmance GPU-to-CPU Transpilation and Optimization via High-L | ovol  |

| , | Ü           |         | nstructs                                                    | 224   |

|   | 9.1         |         | action                                                      |       |

|   | 9.2         |         | round                                                       |       |

|   | 7.2         | 9.2.1   | GPU Compilation                                             |       |

|   |             | 9.2.2   | MLIR Infrastructure                                         |       |

|   |             | 9.2.3   | Polygeist                                                   |       |

|   | 9.3         |         | ach                                                         |       |

|   | <b>,.</b> e | 9.3.1   | Barrier Semantics                                           |       |

|   |             | 9.3.2   | Barrier Lowering                                            |       |

|   | 9.4         |         | el Optimization                                             |       |

|   |             | 9.4.1   | Barrier Elimination & Motion                                |       |

|   |             | 9.4.2   | Memory-to-register promotion across barriers                |       |

|   |             | 9.4.3   | Parallel loop-invariant code motion                         |       |

|   |             | 9.4.4   | Block Parallelism Optimizations                             |       |

|   | 9.5         |         | UDA: Integration into PyTorch                               |       |

|   |             |         | ition                                                       | . 240 |

|    |      | 9.6.1   | Comparison to MCUDA                            | 242 |

|----|------|---------|------------------------------------------------|-----|

|    |      | 9.6.2   | Use case 1: Rodinia Benchmarks                 | 242 |

|    |      | 9.6.3   | Use case 2: Pytorch/Resnet50 Test              | 244 |

|    | 9.7  | Related | d Work                                         | 248 |

|    |      | 9.7.1   | GPU to CPU Synchronization                     | 248 |

|    |      | 9.7.2   | Parallel Portablity/IR, & OpenMP Optimizations | 249 |

|    |      | 9.7.3   | Barriers                                       | 250 |

|    | 9.8  | Conclu  | sion                                           | 251 |

| 10 | "Hea | der-tin | ne" Optimization                               | 252 |

|    | 10.1 | Introdu | uction                                         | 252 |

|    |      | 10.1.1  | Contributions & Overview                       | 254 |

|    | 10.2 | Related | d Work                                         | 254 |

|    | 10.3 | Header  | -Time Optimization                             | 256 |

|    |      | 10.3.1  | Attributes                                     | 257 |

|    |      | 10.3.2  | Attribute Generation                           | 257 |

|    |      | 10.3.3  | Inter-Translation-Unit Data Flow Analysis      | 260 |

|    | 10.4 | Evalua  | tion                                           | 262 |

|    |      | 10.4.1  | Setup                                          | 263 |

|    |      | 10.4.2  | Speedup Potential                              | 263 |

|    |      | 10.4.3  | Speedup Cost                                   | 265 |

|    | 10.5 | Conclu  | sion                                           | 266 |

| 11 | Conc | cluding | Thoughts                                       | 267 |

# **List of Figures**

| 1-1  | Building abstractions once within the compiler enables fast and compos-     |    |

|------|-----------------------------------------------------------------------------|----|

|      | able code to be automatically generated for all user programs               | 30 |

| 2-1  | A function that GCC, ICC, and Cilk Plus/LLVM all fail to optimize effec-    |    |

|      | tively                                                                      | 33 |

| 2-2  | Comparison between a traditional CFG with symmetric parallelism and         |    |

|      | Tapir's CFG with asymmetric parallelism                                     | 35 |

| 2-3  | Code changes required to implement the Tapir/LLVM prototype                 | 37 |

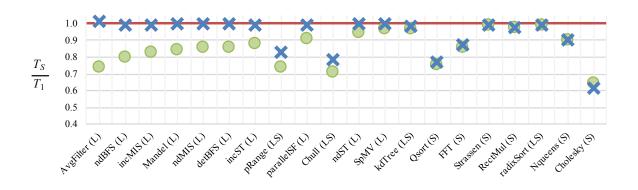

| 2-4  | Graph of work efficiency comparison between Reference and Tapir/LLVM.       | 40 |

| 2-5  | Tapir CFG for the parallel loops in Figure 2-1                              | 46 |

| 2-6  | Example of common-subexpression elimination on a Cilk program               | 50 |

| 2-7  | Example of tail-recursion elimination on a parallel quicksort program       | 52 |

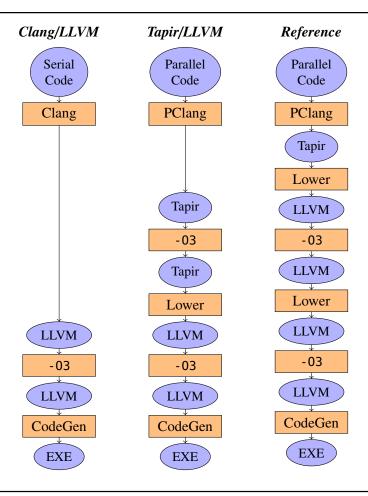

| 2-8  | The compilation pipelines for Clang/LLVM, Tapir/LLVM, and Reference         | 56 |

| 2-9  | Descriptions of the 20 benchmarks used to evaluate Tapir/LLVM               | 57 |

| 2-10 | Numbers for performance comparison between Reference and Tapir/LLVM.        | 62 |

| 3-1  | Simplified EBNF syntax for core TC. Parentheses denote inline alterna-      |    |

|      | tives, brackets denote optional clauses, angle brackets contain textual de- |    |

|      | scriptions used for simplicity                                              | 69 |

| 3-2  | The JIT compilation flow lowers TC to Halide-IR, then to Polyhedral-IR,     |    |

|      | followed by optimization, code generation and execution                     | 70 |

| 3-3  | Optimization steps for sgemm                                                | 73 |

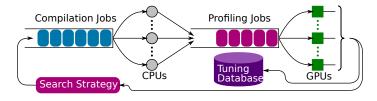

| 3-4  | Multithreaded autotuning pipeline for kernels                               | 82 |

| 3-5  | Example of embedded usage in C++/ATen                                       | 84 |

| 3-6  | Example of embedded usage in PyTorch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3-7  | TC Benchmarks used in the experiments. Evaluated sizes are available in  Table 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3-8  | Source of one full WaveNet cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

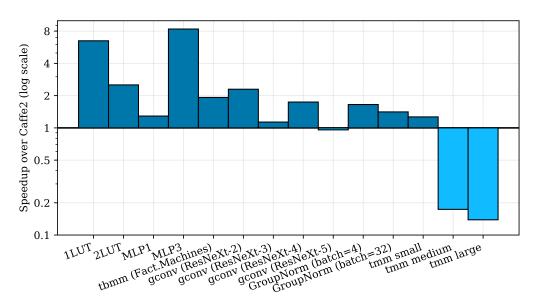

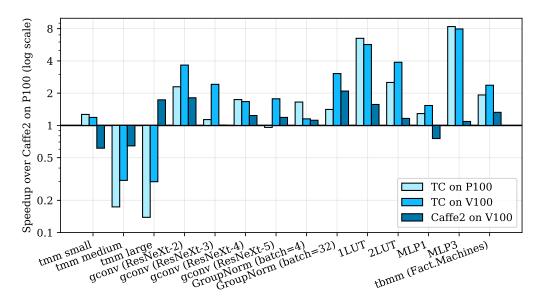

| 3-9  | Speedup of TC-generated kernels over Caffe2 hand-tuned kernels on Quadro P100-12GB                                                                                                                                                                                                                                                                                                                                                                                                                                        |

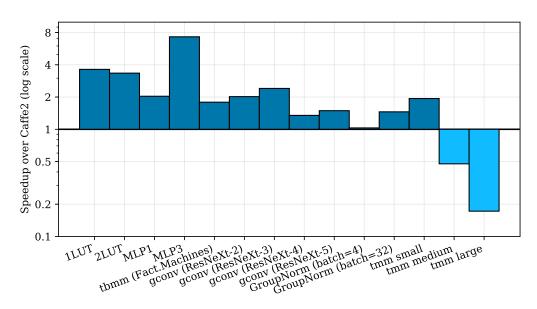

| 3-10 | Speedup of TC-generated kernels over Caffe2 hand-tuned kernels on Tesla V100-SXM2-16GB                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3-11 | Relative performance: baseline is Caffe2 performance on a P100 GPU 88                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4-1  | A simple program to normalize a vector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4-2  | Progressively applying LICM (left) then inlining (right) to the code in Figure 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4-3  | Progressively applying inlining (left) then LICM (right) to the code in Figure 4-1                                                                                                                                                                                                                                                                                                                                                                                                                                        |

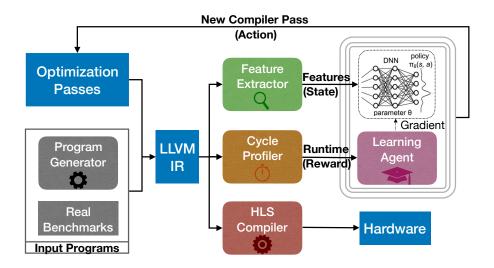

| 4-4  | The block diagram of AutoPhase. The input programs are compiled to an LLVM IR using Clang/LLVM. The feature extractor and clock-cycle profiler are used to generate the input features (state) and the runtime improvement (reward), respectively from the IR. The input features and runtime improvement are fed to the deep RL agent as in input data to train on. The RL agent predicts the next best optimization passes to apply. After convergence, the HLS compiler is used to compile the LLVM IR to hardware RTL |

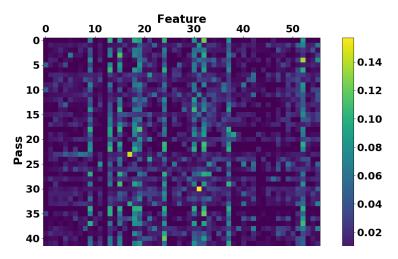

| 4-5  | Heat map illustrating the importance of feature and pass indices                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

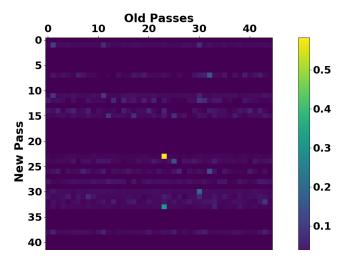

| 4-6  | Heat map illustrating the importance of indices of previously applied passes and the new pass to apply                                                                                                                                                                                                                                                                                                                                                                                                                    |

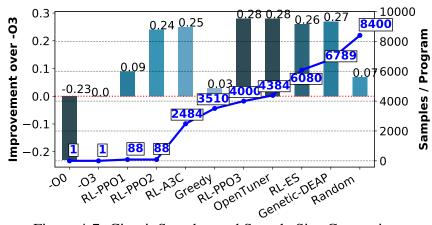

| 4-7  | Circuit Speedup and Sample Size Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

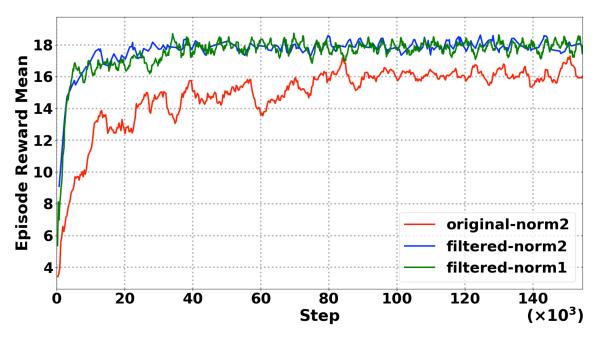

| 4-8 | Episode reward mean as a function of step for the original approach where           |

|-----|-------------------------------------------------------------------------------------|

|     | we use all the program features and passes and for the filtered approach            |

|     | where we filter the passes and features (with different normalization tech-         |

|     | niques). Higher values indicate faster circuit speed                                |

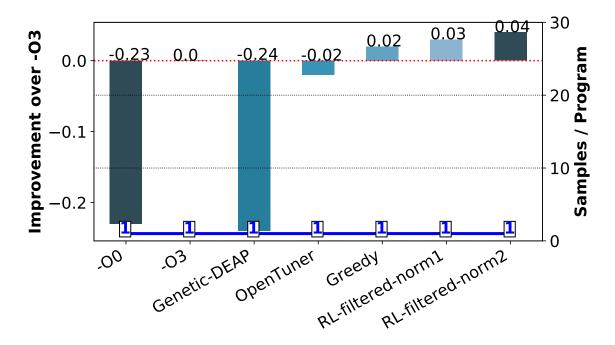

| 4-9 | Circuit Speedup and Sample Size Comparison for deep RL Generalization. 119          |

| 5-1 | <b>Top:</b> An $O(N^2)$ function norm which normalizes a vector. Running loop-      |

|     | invariant-code-motion (LICM) [275, Sec. 13.2] moves the $O(N)$ call to mag          |

|     | outside the loop, reducing norm's runtime to $O(N)$ . Left: An $O(N)$ $\nabla$ norm |

|     | resulting from running LICM before AD. Both mag and its adjoint $\nabla$ mag are    |

|     | outside the loop. <b>Right:</b> An $O(N^2)$ Vnorm resulting from running LICM       |

|     | after AD. $\nabla$ mag remains inside the loop as it uses a value computed inside   |

|     | the loop, making LICM illegal                                                       |

| 5-2 | Top: Call to memcpy for an unknown 8-byte object. Left: Gradient for a              |

|     | memcpy of 8 bytes of double data. <i>Right:</i> Gradient for a memcpy of 8 bytes    |

|     | of float data                                                                       |

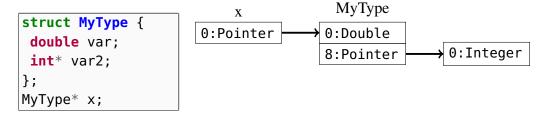

| 5-3 | An example TypeTree used by Type Analysis. The variable x (declared on              |

|     | the left) is a pointer type, which points to a struct MyType, which contains        |

|     | a double at byte 0, and then a pointer at byte 8. That nested pointer points        |

|     | to an integer                                                                       |

| 5-4 | Left: Caching the result of read for the reverse pass. Right: Creating an           |

|     | augmented forward pass for a function to ensure requisite values are cached         |

|     | for the reverse                                                                     |

| 5-5 | Example gradient synthesis for $relu(pow(x,3))$ . The left hand side shows          |

|     | the LLVM IR for the original computation. In the comments on the left we            |

|     | show the shadow allocations of active variables that would be added to              |

|     | the forward pass. The right hand side shows the reverse pass that Enzyme            |

|     | would generate. The full synthesized gradient function would combine                |

|     | these (with shadow allocations added), replacing the return in if.end with          |

|     | a branch to reverse if.end                                                          |

| 5-6  | <i>Left:</i> Specifying a custom forward and reverse pass for f. <i>Right:</i> Creating |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | a gradient for func with $x$ as an active variable and $y$ as a constant                | 130 |

| 5-7  | Left: A simple scalar function computing a Taylor expansion. Center: The                |     |

|      | runtime of the gradient as computed by Enzyme.jl and two common Julia                   |     |

|      | AD frameworks. Right: How Enzyme can be embedded in existing AD                         |     |

|      | frameworks to use Enzyme's efficient implementation of scalars                          | 131 |

| 5-8  | <i>Top:</i> Sample glue code for using Enzyme to produce a custom operator for          |     |

|      | an ML framework. Left & Right: Sample code of using Enzyme to provide                   |     |

|      | gradients of foreign code in PyTorch and TensorFlow, respectively                       | 132 |

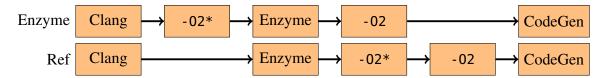

| 5-9  | The pipelines Enzyme and Ref, which run optimizations before and af-                    |     |

|      | ter AD, respectively. The goal of running optimizations prior to AD is                  |     |

|      | to reduce work and simplify the code. The first round of optimizations                  |     |

|      | (-02*) disables scheduling passes such as vectorization or unrolling that               |     |

|      | make heuristic decisions based on the current code size and machine at-                 |     |

|      | tributes. Scheduling optimizations are included in the second round of op-              |     |

|      | timizations (-02) when the entire code (including gradient) is available                | 133 |

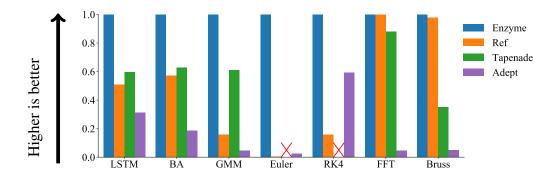

| 5-10 | Relative speedup of different AD systems on the benchmark suite, higher                 |     |

|      | is better. A red X is used to denote a system not being compatible with                 |     |

|      | the benchmark (Tapenade only supports C and not C++ programs). For                      |     |

|      | each benchmark, we take the geometric mean of the run time for all test                 |     |

|      | cases, normalizing to the victor. A value of 1.0 denotes the fastest AD                 |     |

|      | system tested for that benchmark, whereas a value of 0.5 denotes that an                |     |

|      | AD system produced a gradient which took twice as long                                  | 133 |

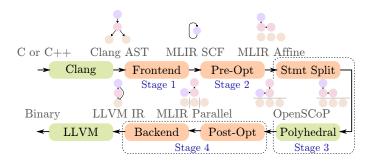

| 6-1  | Polygeist flow consists of 4 stages. The frontend traverses Clang AST to                |     |

|      | emit MLIR SCF dialect (Section 6.3.1), which is raised to the Affine dialect            |     |

|      | and pre-optimized (Section 6.3.2). The IR is then processed by a polyhe-                |     |

|      | dral scheduler (Sections 6.3.3,6.3.4) before post-optimization and paral-               |     |

|      | lelization (Section 6.3.5). Finally, it is translated to LLVM IR for further            |     |

|      | optimization and binary generation by LLVM                                              | 137 |

|      |                                                                                         |     |

| 6-2  | Generic MLIR syntax for an operation with two operands, one result, one      |     |

|------|------------------------------------------------------------------------------|-----|

|      | attribute and a single-block region                                          | 139 |

| 6-3  | Polynomial multiplication in MLIR using Affine and Standard dialects         | 141 |

| 6-4  | Type correspondence between C, LLVM IR and MLIR types                        | 143 |

| 6-5  | Example demonstrating Polygeist ABI. For functions expected to be com-       |     |

|      | piled with Polygeist such as setArray, pointer arguments are replaced        |     |

|      | with memref's. For functions that require external calling conventions       |     |

|      | (such as main/strcmp), we fall back to using llvm.ptr and generating         |     |

|      | conversion code where appropriate                                            | 147 |

| 6-6  | Polygeist breaks region-spanning use-def chains and handles multi-use val-   |     |

|      | ues by introducing scratchpad storage when operation duplication is illegal. |     |

|      | In absence of motion-barrier statement, the %0 load would be duplicated      |     |

|      | and sunk. Pseudo-MLIR with types and braces omitted for brevity              | 149 |

| 6-7  | Outlining makes polyhedral "statements" visible in code from Fig. 6-6        | 150 |

| 6-8  | Splitting a nested reduction statement (top) into a fully parallel compute   |     |

|      | statement and a trivial reduction statement (bottom left) makes Pluto gen-   |     |

|      | erate different schedules (bottom right). Further scratchpad array expansion |     |

|      | may enable loop fission and give scheduler even more liberty                 | 152 |

| 6-9  | Polygeist detects memory locations accessed in all loop iterations, e.g. re- |     |

|      | duction accumulators such as %r1[0] and transforms them to loop-carried      |     |

|      | values (secondary induction variables), except when computed with side-      |     |

|      | effects, interleaved stores or by non-associative/commutative operations     | 155 |

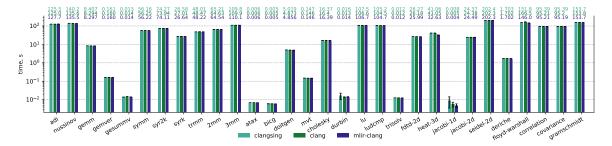

| 6-10 | Mean and 95% confidence intervals (log scale) of program run time across     |     |

|      | 5 runs of Polybench in Clang, ClangSing and MLIR-Clang configurations,       |     |

|      | lower is better. The run times of code produced by Polygeist without op-     |     |

|      | timization is comparable to that of Clang. No significant variation is ob-   |     |

|      | served between single and double optimization. Short-running jacobi-1d       |     |

|      | shows high intra-group variation                                             | 157 |

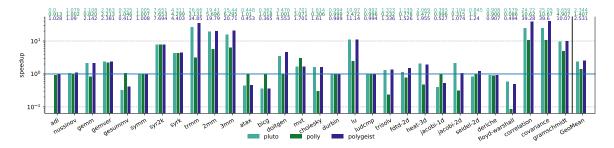

| 6-11 | Median speedup over Clang for sequential configurations (log scale), higher      |     |

|------|----------------------------------------------------------------------------------|-----|

|      | is better. Polygeist outperforms (2.53× geomean speedup) both Pluto (2.34×)      |     |

|      | and Polly (1.41×) on average. Pluto can't process adi, which is therefore        |     |

|      | excluded from summary statistics                                                 | 158 |

|      |                                                                                  |     |

| 6-12 | Median speedup over Clang for parallel configurations (log scale), higher        |     |

|      | is better. Polygeist outperforms (9.47× geomean speedup) both Pluto (7.54×)      |     |

|      | and Polly (3.26×) on average. Pluto can't process adi, which is therefore        |     |

|      | excluded from summary statistics                                                 | 158 |

|      |                                                                                  |     |

| 6-13 | Excerpt from the deriche benchmark. The outer loop reuses ym1 which              |     |

|      | makes it appear non-parallel to affine schedulers (left). Polygeist detects      |     |

|      | parallelism thanks to its mem2reg optimization, reduction-like loop-carried      |     |

|      | %ym1 value detection and late parallelization (right)                            | 161 |

|      |                                                                                  |     |

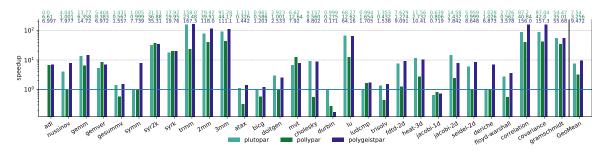

| 6-14 | Mean and 95% confidence intervals of run time across 5 runs of Polybench         |     |

|      | where statement splitting is applicable (Section 6.3.4), lower is better. It re- |     |

|      | sults in faster run time (geomean 1.28× sequential, 1.39× parallel speedup)      |     |

|      | except for sequential 2mm ( $-4\%$ ) and parallel trmm ( $-9\%$ )                | 162 |

|      |                                                                                  |     |

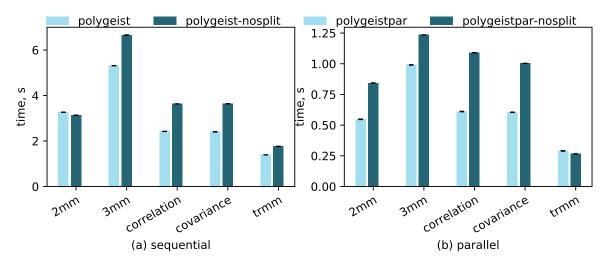

| 6-15 | Reduction parallelization allows PolygeistPar to produce larger speedups         |     |

|      | and at smaller sizes than PollyPar and PolyGeistPar without reduction sup-       |     |

|      | port. PlutoPar fails to parallelize leading to no speedup                        | 163 |

|      |                                                                                  |     |

|      |                                                                                  |     |

| 7-1  | A parallel initialize function (top) with a naive reverse mode AD gradient       |     |

|      | function (bottom) that does not take the parallelism into account. Conse-        |     |

|      | quently, the concurrent read of the variable val causes a race in the reverse-   |     |

|      | mode gradient computation                                                        | 160 |

| 7-2 | Rules for memory operations. Shadow registers d_res and d_val are thread-local since they shadow thread-local registers. There is no risk of racing on thread-local data and no special handling required. Both ptr and shadow d_ptr might be raced on and require atomics in the adjoint of the load. If ptr (and consequently d_ptr) is proven to be thread-local or have constant memory, the atomic update can be replaced with a serial update or                   | 174   |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|     | reduction, respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 1/4 |

| 7-3 | Illustrations for the case analysis of the barrier instruction adjoint definition.                                                                                                                                                                                                                                                                                                                                                                                       | . 175 |

| 7-4 | A simple GPU function, inner, that is differentiated by Enzyme within the CUDA kernel $\nabla$ kernel (top). A high-level representation of the synthesized gradient Enzyme would generate is shown as $\nabla$ inner (bottom). The call toenzyme_autodiff is replaced by a call to the newly generated derivative function                                                                                                                                              | . 179 |

| 7-5 | In (a), there is a sample program that uses values of an array in a loop nest. The loads of the array cannot be hoisted by LICM. The array is overwritten outside of the loop nest. Enzyme would require caching a value for every execution of the load instruction, as shown in (b) and using $\Theta(NM)$ memory. Using the cache LICM optimization, the cache could be hoisted outside the loop as shown in (c), requiring only $\Theta(M)$ memory                   | . 180 |

| 7-6 | (a) A sample program that loads two variables x and y and then perform some computation with the result. These variables are subsequently overwritten and thus would require caching to be available in the reverse pass. A naive cache algorithm would produce the code in (b) in which both overwritten memory locations x and y are cached. As shown in (c), one could instead cache the sum since neither x nor y is individually necessary to compute the gradient. | . 182 |

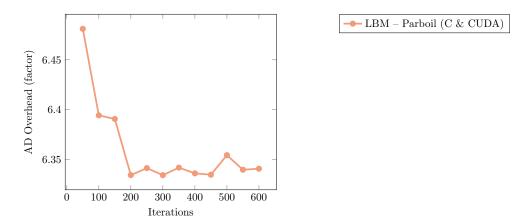

| 7-7  | AD overhead of the benchmark applications, as compared with a single              |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | evaluation of the forward pass. An overhead of $N$ can be read as saying          |     |

|      | that collecting the gradients of all inputs (as well as running the original      |     |

|      | code) is equivalent to running the original code $N$ times                        | 187 |

| 7-8  | Simplified version of the computation within LBM. The kern function               |     |

|      | calls a GPU kernel that iterates the simulation one timestep forward in time,     |     |

|      | storing the result in dst. The lbm CPU function calls the GPU kernel until        |     |

|      | all iterations have completed. The iteration must happen outside the ker-         |     |

|      | nel to ensure that all threads from one timestep have completed prior to          |     |

|      | performing another timestep                                                       | 187 |

| 7-9  | Differentiation of the combined CPU+GPU computation in LBM. The code              |     |

|      | in (a) represents host code, which differentiates the overall function lbm,       |     |

|      | defined in Figure 7-8. The kern function is annotated with custom forward         |     |

|      | and reverse passes aug_kern and rev_kern. These functions allocate a              |     |

|      | <pre>tape and call the aug_streamCollide and rev_streamCollide kernels,</pre>     |     |

|      | which are generated by Enzyme in (b)                                              | 188 |

| 7-10 | Overhead of selectively disabling AD and GPU-specific optimizations de-           |     |

|      | scribed in Section 7.5. OOM indicates running out of memory or an in-             |     |

|      | definite runtime. Each dot represents the overhead of AD compared to the          |     |

|      | forward pass alone                                                                | 190 |

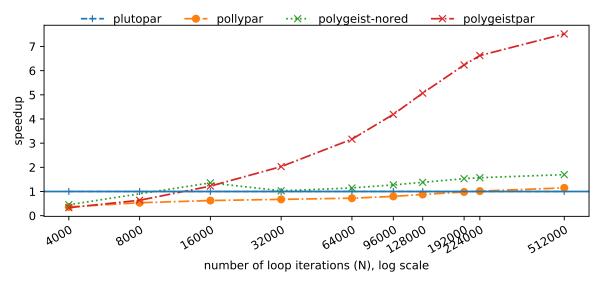

| 7-11 | Overhead of Enzyme compared with the forward pass as the problem size             |     |

|      | and number of threads increase, with constant work per thread                     | 193 |

| 7-12 | Overhead of Enzyme compared with the forward pass where work is in-               |     |

|      | creased while maintaining a constant number of threads                            | 194 |

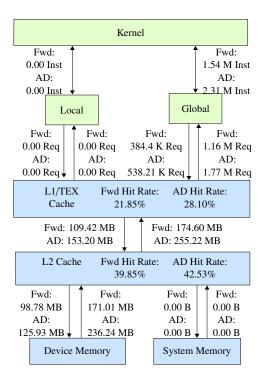

| 7-13 | Memory workload analysis for LULESH at size 135 <sup>3</sup> comparing the origi- |     |

|      | nal code (Fwd) to the gradient (AD)                                               | 195 |

| 7-14 | Compile time in seconds of the source file with and without derivatives           | 196 |

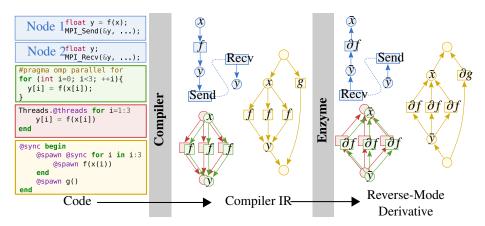

| 8-1 | The compiler lowers the various parallel programming languages (left) into        |      |

|-----|-----------------------------------------------------------------------------------|------|

|     | a common representation (center). Some constructs such as Julia tasks and         |      |

|     | OpenMP worksharing loops may result in an almost identical representa-            |      |

|     | tion. The automatic differentiation rules in Enzyme can be written for the        |      |

|     | intermediate representation, greatly simplifying the generation of reverse-       |      |

|     | mode derivatives (right) for the input languages and constructs, and further      |      |

|     | enabling compiler-optimizations                                                   | 200  |

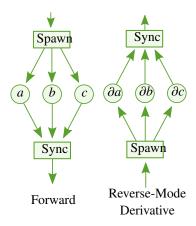

| 8-2 | Illustration of Correctness for Parallel AD: The control and data flow is re-     |      |

|     | versed, hence inverting the data- and control flow. In the forward pass (left)    |      |

|     | the control flow goes from spawn to sync. In the reverse-mode derivative          |      |

|     | (right), the locations of spawn and sync are reversed                             | 204  |

| 8-3 | Left: An OpenMP function which squares an element of an array on each             |      |

|     | thread. <i>Right:</i> The compiler lowers this construct to a closure outlined of |      |

|     | the body and a call to thekmpc_fork runtime call which runs the closure           |      |

|     | on each thread.                                                                   | 205  |

| 8-4 | Left: Gradient of square (ref. Figure 8-3). This calls the OpenMP parallel        |      |

|     | runtime call twice, once for the forward pass, and once for the reverse pass.     |      |

|     | <i>Right:</i> The forward and reverse passes of the outlined OpenMP parallel body | .207 |

| 8-5 | An asynchronous MPI send request and its corresponding derivative. Since          |      |

|     | the derivative of the wait must know what type of instruction it synchro-         |      |

|     | nized in order to spawn of its corresponding adjoint in the reverse, the re-      |      |

|     | quest type is stored in the shadow request in the forward pass. A full MPI        |      |

|     | program would also need to call an analagous recv and derivative on the           |      |

|     | destination node                                                                  | 208  |

| 8-6 | Top Left: An OpenMP function that uses firstprivate memory to set the first       |      |

|     | iteration handled by each thread to in, the remainder to 0. Bottom Left: An       |      |

|     | explicit version of the code on the top left, with firstprivate being replaced    |      |

|     | with an equivalent thread-local in_local. <i>Right:</i> C code representing the   |      |

|     | gradient generated by Enzyme                                                      | 210  |

| 8-7  | A manual user-written min reduction, as simplified from its use from the     |

|------|------------------------------------------------------------------------------|

|      | CalcCourantConstraintForElems and CalcHydroConstraintForElems                |

|      | functions in LULESH. While this could be rewritten to use higher-level re-   |

|      | duction routines which can be handled by both Enzyme and other tools,        |

|      | differentiating it "as-is" requires correct handling of a variety of OpenMP  |

|      | constructs                                                                   |

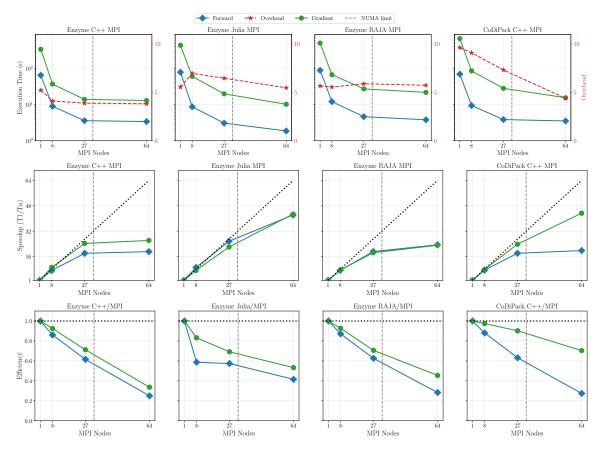

| 8-8  | <b>Top Row:</b> Runtime for 10 iterations of the LULESH proxy-benchmark      |

|      | for the different implementations. The number of processors is increased,    |

|      | while the overall problem size stays fixed. We used the following task       |

|      | count-block size combinations: 1:192, 8:96, 27:64, and 64:48. Middle         |

|      | Row: Strong scaling behavior. Bottom Row: Weak scaling behavior. The         |

|      | number of processors is increased, while the per-processor problem size      |

|      | stays fixed. The block size used was 48                                      |

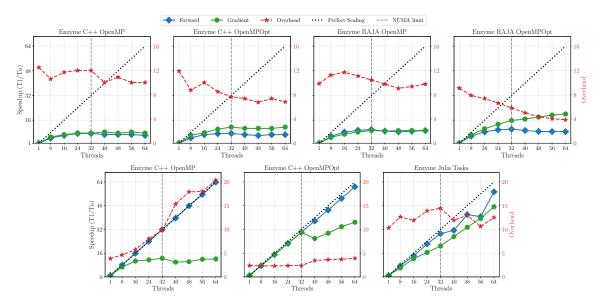

| 8-9  | Thread parallelism strong scaling on the LULESH (Top Row) and BUDE           |

|      | (Bottow Row) proxy-benchmarks for the different evaluated implementa-        |

|      | tions. The number of available processors is increased, while the overall    |

|      | problem size stays fixed. The block size used for LULESH was 96 and the      |

|      | default number of poses was used for BUDE                                    |

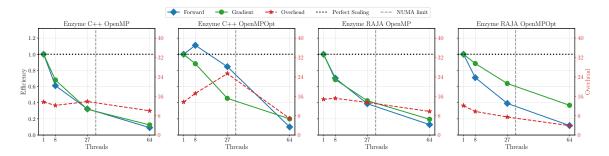

| 8-10 | Thread parallelism weak scaling on the LULESH proxy-benchmarks for           |

|      | the different evaluated implementations. The number of available proces-     |

|      | sors is increased, while the problem size per processor stays fixed. We used |

|      | the following thread count-block size combinations: 1:24, 8:48, 27:72, and   |

|      | 64:96                                                                        |

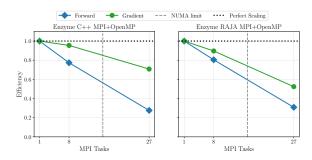

| 8-11 | Efficiency of LULESH when running with 1 8, and 27 MPI ranks, 2 OpenMP       |

|      | threads, and a block size of 48                                              |

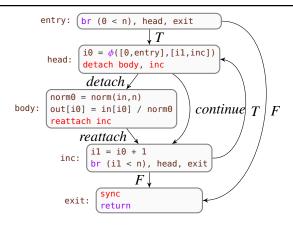

| 9-1 | A sample CUDA program normalize, which normalizes a vector and the             |     |

|-----|--------------------------------------------------------------------------------|-----|

|     | CPU function launch launching the kernel. Each GPU threads calls sum,          |     |

|     | resulting in $O(N^2)$ work. Using shared memory (commented) reduces the        |     |

|     | work to $O(N^2/B)$ at extra resource cost. Computing sum before the kernel     |     |

|     | reduces work to $O(N)$                                                         | 227 |

| 9-2 | Polygeist/MLIR equivalent of launch/normalize code from Figure 9-1.            |     |

|     | The kernel call is available directly in the host code which calls it. The     |     |

|     | parallelism is explicit with parallel for loops across the blocks and threads. |     |

|     | Shared memory is placed within the block parallel for, allowing access         |     |

|     | from any thread in the same block, but not a different block                   | 228 |

| 9-3 | Left: A program containing a barrier between two arbitrary instructions.       |     |

|     | Right: Barrier semantics can be refined memory addresses accessed by           |     |

|     | operations above/below it in all threads <i>except</i> the current one         | 230 |

| 9-4 | Parallel loop splitting around a barrier: the code above the barrier is placed |     |

|     | in a separate parallel "for" loop from the code following the barrier. This    |     |

|     | transformation eliminates the barrier, while preserving the semantics. The     |     |

|     | min-cut algorithm stores %x and %y, which are then used to recompute %a,       |     |

|     | %b, and %c in the second loop                                                  | 232 |

| 9-5 | Left: A shared memory addition, which consists of a kernel call which          |     |

|     | contains for loop with a barrier inside. Right: Same but with the barrier      |     |

|     | directly in the parallel loop after a parallel/serial loop interchange         | 233 |

| 9-6 | Parallel interchange around a while loop. As the condition() function          |     |

|     | call must be executed on each thread to preserve correctness, a helper vari-   |     |

|     | able is used which holds the value of the call on the first thread             | 234 |

| 9-7 | An example CUDA kernel from the Rodinia backprop test that contains            |     |

|     | unnecessary synchronization and unnecessary use of shared memory               | 236 |

| 9-8 | Example of OpenMP parallel region fusion. Fuse two adjacent OpenMP             |     |

|     | parallel regions by inserting a barrier to allow the threads to be initialized |     |

|     | once instead of twice                                                          | 239 |

| 9-9  | Example of OpenMP parallel region hoisting. This can be seen as an ex-           |

|------|----------------------------------------------------------------------------------|

|      | tension of parallel region fusion across "regions" corresponding to each         |

|      | iteration of the outer loop                                                      |

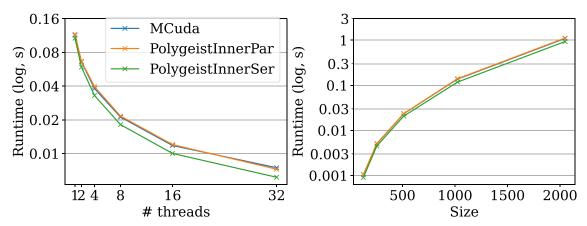

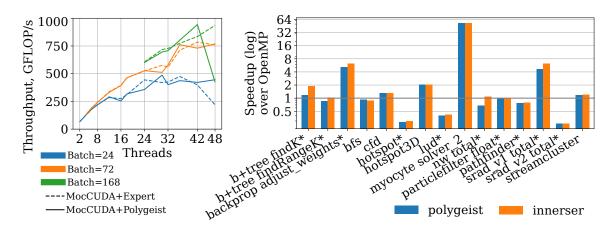

| 9-10 | PolygeistInnerPar performs similarly to MCUDA; PolygeistInnerSer out-            |

|      | performs MCUDA. PolygeistInnerSer disables inner loop parallelization            |

|      | similaly to MCUDA, whereas PolygeistInnerPar keeps both the blocks and           |

|      | threads parallel. Left: Average runtime as a function of thread count (av-       |

|      | eraging over matrix sizes). Right: Average runtime as a function of matrix       |

|      | size (averaging over thread counts)                                              |

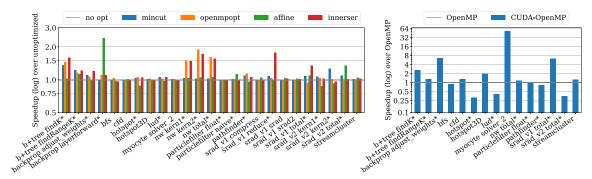

| 9-11 | Left: Relative speedup (higher is better) applying parallel optimizations,       |

|      | proposed in Section 9.4, over our flow without optimization. Right: Speedup      |

|      | of transpiled CUDA-to-OpenMP compared against native OpenMP code                 |

|      | (when available) running with 32 threads. Asterisks denote barriers within       |

|      | the benchmark                                                                    |

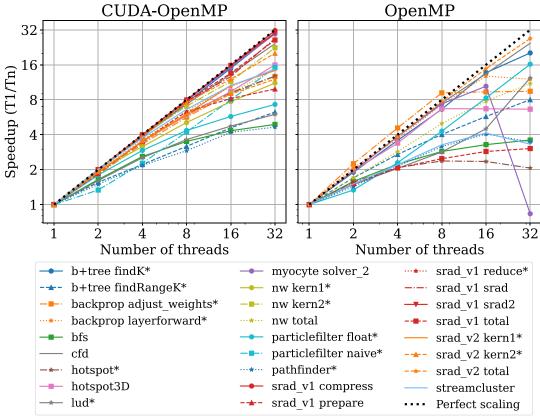

| 9-12 | Scaling behavior of CUDA Rodinia kernels, when run on the CPU                    |

|      | with OpenMP, and OpenMP Rodinia kernels (where available), using 32              |

|      | threads. Not all Rodinia CUDA kernels have OpenMP versions                       |

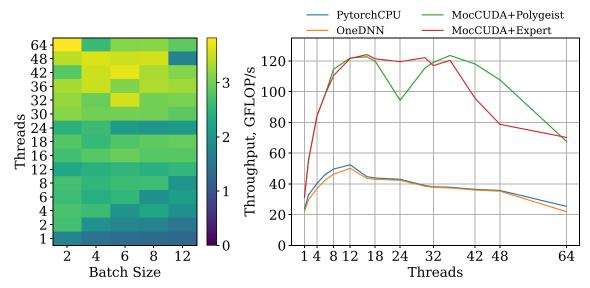

| 9-13 | ResNet50 training on Fugaku node. Left: heatmap of relative throughput           |

|      | increase of "MocCUDA+Polygeist" over Fujitsu-tuned oneDNN, higher is             |

|      | better. Right: geomean throughput across batch sizes; "MocCUDA+Expert"           |

|      | uses an expert-written OpenMP kernel; "MocCUDA+Polygeist" uses the               |

|      | generated kernel, and PytorchCPU is Pytorch's native OpenMP backend 246          |

| 9-14 | Left: ResNet throughput continues to scale for large batch sizes; large          |

|      | batches time out with few threads. Right: inner loop serialization con-          |

|      | tributes up to 30% speedup while most comes from barrier optimizations 24'       |

| 10-1 | A file with a function definition (norm) and a function declaration (mag). As    |

|      | the latter is opaque, it is illegal to move the call outside the loop, resulting |

|      | in a runtime of $O(N^2)$                                                         |

| 10-2 | cessfully hoist the call outside the loop and reduce the runtime to $O(N)$ .                                                                                                                                                                                                                                                                                                                                                                                |       |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 253 |

| 10-3 | Remark Mode: We leverage existing functionality [246] to emit optimization remarks listing the attributes that were deduced for functions, parameters, and return values. Remarks can be printed for human consumption, dumped to machine readable formats, or viewed in graphical tools where remarks are displayed at the source locations                                                                                                                | . 258 |

| 10-4 | HTO derived that the function sum is readnone, indicating that it doesn't read any memory. Given that sum should return the sum of all elements in an array, this is definitely a bug as it cannot produce a correct output without reading the array                                                                                                                                                                                                       | . 258 |

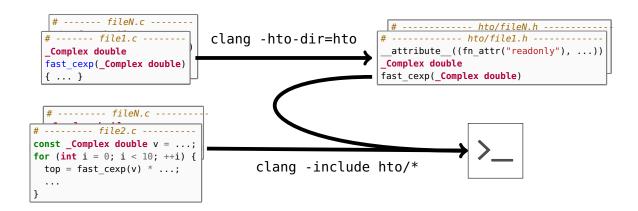

| 10-5 | Header Mode: Single-App. Through the -hto-dir flag a header files for each source file is generated. The header contains an augmented function declaration for each externally visible function definition in the input. In subsequent compilations those headers can be easily included to expose optimization opportunities, e.g. to allow hoisting of readonly calls out of loops, similar to the motivation example in Figure 10-2                      | . 260 |

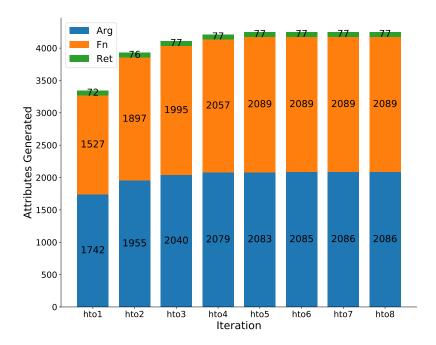

| 10-6 | The y-axis shows the number and kind of attributes in HTO headers for the <i>musl</i> standard C library [115]. The x-axis show how recompilation using the existing HTO generated headers and producing new augmented headers changes these numbers until a fixpoint state is reached. Note that we exclude 1558 unwind and strictfp function attributes from these graphs as they are added to <i>all</i> functions due to the compilation configuration. | . 261 |

| 10-7 | The kind and number of LLVM-IR attributes [82] derived for the musl              |    |

|------|----------------------------------------------------------------------------------|----|

|      | standard C library [115]. The hto1 column describes the first compilation        |    |

|      | with HTO, hence the attributes produced without any existing HTO head-           |    |

|      | ers. The hto8 column shows the fixpoint state after 7 recompilations in          |    |

|      | which prior HTO results have been used and new augmented HTO headers             |    |

|      | have been produced. The left table shows a selection of relevant parame-         |    |

|      | ter attributes and the right table lists selected function attributes. Note that |    |

|      | nounwind and strictfp are listed here for reference while it is eliminated       |    |

|      | from Figure 10-6, all functions have that attribute by construction 20           | 63 |

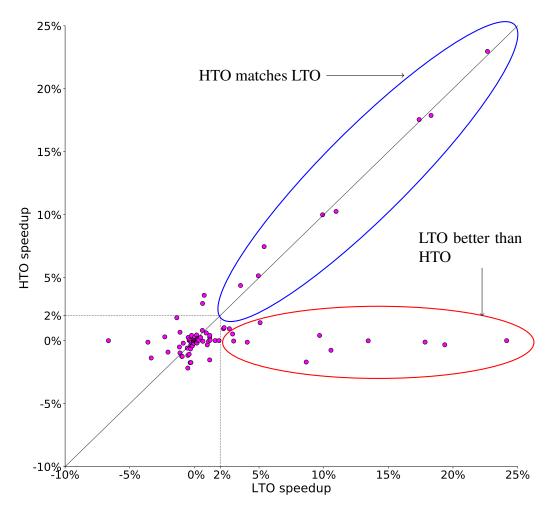

| 10-8 | Speedup of HTO (y-axis) and thin-LTO (x-axis) against vanilla LLVM for           |    |

|      | the multi-source tests in the LLVM test suite. The box encloses all tests        |    |

|      | with less than 4% performance difference. The blue oval highlight tests          |    |

|      | that have a significant speedup for both HTO and thin-LTO. The red oval          |    |

|      | highlights tests where LTO achieves a speedup not found by HTO 20                | 64 |

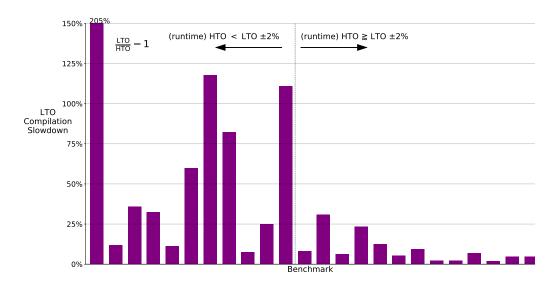

| 10-9 | Compile-time overhead of LTO and HTO on codes where a speedup exists.            |    |

|      | Codes on the left have the greatest speedup on LTO and not HTO, whereas          |    |

|      | codes on the right have the greatest speedup on both LTO and HTO 20              | 65 |

## Chapter 1

## Introduction

The end of Moore's law and the increasing reliance on computation has led to an explosion of complex software packages and hardware architectures in various domains. While this diversity enables an unprecedented level of flexibility in building applications, it also requires rewriting applications to efficiently support each combination of software paradigms (e.g. differentiable, encrypted) and hardware targets. The need for performance and portability has forced domain-experts to spend their time learning about and implementing concepts like GPU reductions or the TensorFlow API, rather than working on their intended problem.

Previous solutions have been proposed and include language extensions (e.g., OpenCL [102], OpenACC [169]), parallel programming frameworks (e.g., Kokkos [63]), and domain-specific languages (e.g., Spiral [314], Halide [319]). All of these approaches still require legacy applications to be ported, and sometimes entirely rewritten, due to differences in the language, or the underlying programming model.

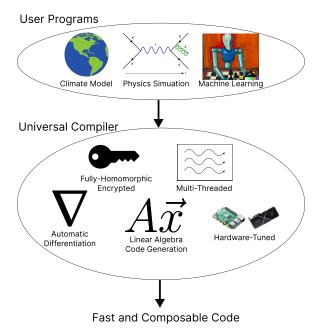

I propose creating high-level abstractions and transformations once within a common multi-purpose compiler that can take existing code and generate optimized code for each software/hardware paradigm, rather than burdening the programmer. In contrast to the mythical "sufficiently smart compiler", my research focuses on explicit domains where preserving information across the library, language, and compiler boundary can be applied to real programs. This design is composable by definition and enables tool-builders to write platform-specific code once, rather than the user writing and maintaining

Figure 1-1: Building abstractions once within the compiler enables fast and composable code to be automatically generated for all user programs.

multiple versions. Further, bringing these semantics together in a single tool enables the compiler to automatically apply cross-package optimizations that would be difficult for even expert programmers to write by hand.

I demonstrate the feasibility of this approach by building several real-world and composable systems in several domains (described below). In addition to each of these compiler abstractions being individually beneficial for performance and usability, the fact that they co-exist in a common compiler framework means that they mutually benefit each other. As an example, both the Tapir representation of parallel programs (Chapter 2) and the Enzyme compiler for differentiating functions (Chapter 5) each individually provide performance benefits. Operating on a common compiler representation for both parallelism and differentiation, however, enables both seamless differentiation of parallel programs and composition of optimizations (Chapter 8). This combined and composable set enables greater performance of parallel differentiation than either parallel-specific optimizations, or differentiation-specific optimizations could provide individually.

Many chapters of this thesis will share variations of a common vector normalization example code (Figures 2-1, 4-1, 4-2, 4-3, 5-1, 9-1, 10-1, 10-2). Individually, each of these

will demonstrate how a system will run (often asymptotically) slower due to its lack of compiler-based domain knowledge. The fact that the same example has a significant performance gap in many different domains (differentiation, parallelism, accelerators, phase ordering, etc) indicates how critical compiler representations are – and also how tricky they are to get right. Besides a stylistic choice to use a similar example throughout the thesis to ease comprehension, there is nothing fundamental about that particular example code that makes it benefit so extensively from a variety of domain optimizations. Instead, I argue that this example indicates that applications in general will tend to benefit from a variety of domain-specific optimizations.

Through the lens of compilers, this thesis will explore fundamental principles to building and efficiently executing modern scientific computing and machine learning applications. Among other topics, thesis will explore compiler representations and transformations for:

- *Parallelism:* leveraging multiple processing units, on the CPU (Chapters 2, 6, 9, 8), GPU/accelerators (Chapters 3, 9, 7), or distributed machines (Chapter 8);

- Automatic differentiation: computing the derivative of program functions (Chapters 5, 7, 8);

- *Scheduling:* finding the fastest versions of programs by optimizing for hardware specifics, like caches, bandwidth, or thread count (Chapters 3, 6);

- *Portability:* enabling programs to run efficiently on different hardware or systems (Chapters 3, 9);

- *Program search:* methods and bottlenecks for automatically finding faster versions of programs (Chapters 4, 10, 3); and

- *Tensor Arithmetic:* efficiently computing fast scalar, vector, matrix, and vector operations (Chapters 3, 6, 9).

<sup>&</sup>lt;sup>1</sup>It is for this reason that the author lovingly refers to this thesis by a secondary title "10 ways to normalize a vector, number 7 will surprise you."

## Chapter 2

# Tapir: A compiler representation for fork-join parallelism

## 2.1 Introduction

Mainstream compilers, such as GCC [366], ICC [193], and LLVM [230] provide linguistic extensions for frameworks such as Cilk Plus[191] and OpenMP [21, 293] that allow programmers to write fork-join parallel programs. Typically in such frameworks, one can specify parallelism at a high level by denoting tasks or loops iterations that may be executed concurrently.

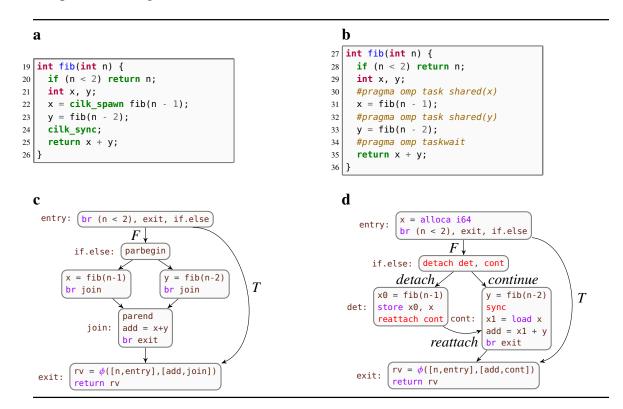

Although these mainstream compilers support fork-join parallelism, they struggle to optimize programs when they encounter such linguistic constructs. Paradoxically this can even mean that programs you'd expect to show large parallel speedups, are slower than the equivalant serial code. Consider, for example, the parallel cilk\_for loop on lines 7–8 in Figure 2-1a, which indicates that iterations of the loop are free to execute in parallel. In a serial version of this loop, where the cilk\_for keyword is replaced by an ordinary for keyword, each of the compilers GCC 5.3.0, ICC 16.0.3, and Cilk Plus/LLVM 3.9.0 observes that the call to mag on line 8 produces the same value in every iteration of the loop, and they optimize the loop by computing this value only once before the loop executes. This optimization dramatically reduces the total time to execute normalize from  $\Theta(n^2)$  to  $\Theta(n)$ .

```

b

a

_attribute__((const))

_attribute__((const))

02 double mag(const double *A, int n);

double mag(const double *A, int n);

12

void normalize(double *restrict out,

void normalize(double *restrict out,

13

const double *restrict in, int n)

14

const double *restrict in, int n) {

#pragma omp parallel for

15

07

cilk_for (int i = 0; i < n; ++i)

for (int i = 0; i < n; ++i)

16

\overline{out[i]} = in[i] / mag(in, n);

08

17

out[i] = in[i] / mag(in, n);

09 }

18 }

```

Figure 2-1: A function that GCC, ICC, and Cilk Plus/LLVM all fail to optimize effectively. **a** A Cilk version of the code. The cilk\_for loop on lines 7–8 allows each iteration of the loop to execute in parallel. The mag function computes the norm of a vector in  $\Theta(n)$  time. The call to mag on line 8 can be safely moved outside of the loop, but none of these three mainstream compilers perform this code motion, even though they all do so when the cilk\_for keyword is replaced with an ordinary for keyword. **b** The corresponding OpenMP code.

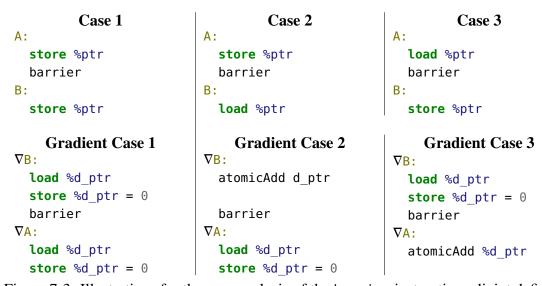

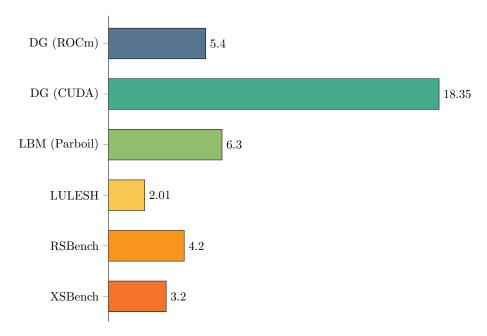

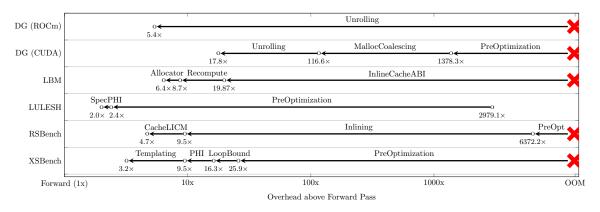

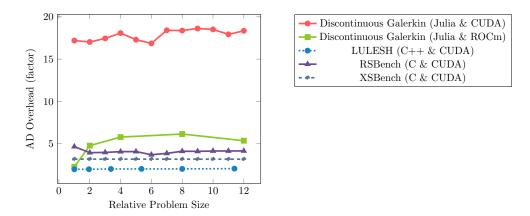

Although this same optimization can, in principle, be performed on the actual parallel loop in the figure, no mainstream compiler performs this code-motion optimization. The same is true when the parallel loop is written using OpenMP, as shown in Figure 2-1b.